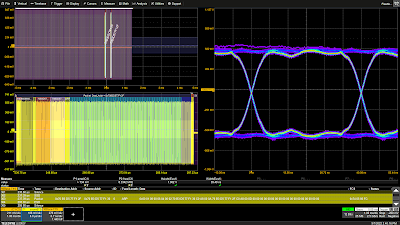

|

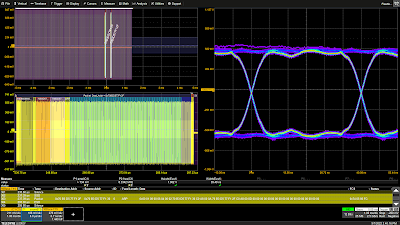

Figure 1. The 10Base-T1S TDME option features

easy eye diagram creation for signal integrity analysis.

Click on any image to enlarge it. |

In addition to special serial data bus measurements of 10Base-T1S signals, the

10Base-T1S Trigger, Decode, Measure/Graph & Eye Diagram (TDME) option automates the generation and display of eye diagrams on Teledyne LeCroy oscilloscopes. Eye diagrams are an important element of serial data analysis, used to understand the signal integrity of the communications network.

The eye diagram is a general-purpose tool for analyzing serial digital communications signals. It shows the effects of additive vertical noise, horizontal jitter, duty cycle distortion, inter-symbol interference, and crosstalk on a serial data stream.

The eye diagram is formed by overlaying repetitive occurrences of slightly more than a single clock period (UI) of a serial data signal on a persistence display which shows the accumulated history of multiple acquisitions, as shown in Figure 1.

Due to the use of Differential Manchester encoding (DME), the 10Base-T1S eye is formed with twice the signal clock rate. The signal shown has a symbol rate of 12.5 Mbps and the eye is clocked at 25 Mbps.