|

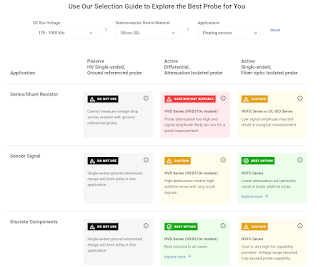

Fig.1, 10Base-T1S PLCA cycle. If there is no data

traffic (top), only BEACONs are seen on the bus.

Data from a node (bottom) will expand the time

between two BEACONs. |

10Base-T1S (IEEE 802.cg) is a variant of

Automotive Ethernet that supports half-duplex and full-duplex

communication, allowing either a point-to-point direct connection between two

nodes, or use of a multidrop topology with up-to-eight nodes connected on a

single 25 m bus segment.

Multidrop cabling of one bus line provides options to extend

and scale with fewer physical wires and less weight than point-to-point topologies. With minimum connector space at the ECU, the bus line can

be expanded simply by adding sensor units. A bus line with additional sensor

units for ultrasonic and short-range radar is an example of how multidrop

cabling can be scaled.

Among the main objectives of the

10Base-T1S PHY layer are reconciliation of transmissions from a variety of

mediums, ensuring cooperative behavior by the nodes on a multidrop bus. One

way it does this is through the use of Physical-Layer Collision Avoidance (PLCA)

technology to minimize dead time and avoid

collisions. In this post, we'll describe the workings of PLCA and in a future post, how you can debug PLCA timing issues using an oscilloscope with the 10Base-T1S TDME software.