|

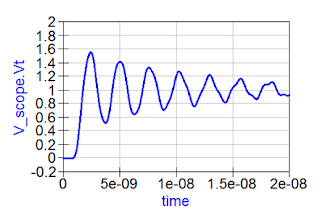

| Figure 1: Characteristic waveform when the source impedance is lower than the cable impedance. |

For this example, the source voltage is a 3.3 V square wave and the source impedance is 9 Ω. As before, our transmission line is a 50 Ω coaxial cable connecting the source to the oscilloscope. If the oscilloscope input termination is set to 1 MΩ, we see the interesting waveform shown in Figure 1.