|

| Figure 1: PLL bandwidth testing ensures that the add-in card's PLL bandwidth and peaking are within specifications |

You need to test, we're here to help.

You need to test, we're here to help.

Showing posts with label PCI-SIG. Show all posts

Showing posts with label PCI-SIG. Show all posts

16 January 2018

PCIe 4.0 PLL Bandwidth Testing

15 January 2018

PCIe 4.0 Receiver Link-Equalization Testing (Part II)

|

| Figure 1: Working out the optimal combination of Tx emphasis presets and receiver CTLE settings |

PCIe 4.0 Receiver Link-Equalization Testing (Part I)

|

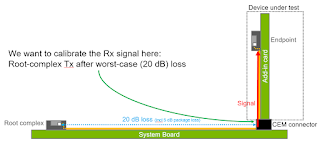

| Figure 1: PCIe 4.0 receiver link-equalization testing takes place at the site of the channel's worst-case signal |

PCIe 4.0 Transmitter Link-Equalization Testing

|

| Figure 1: Shown is an overview of the PCIe 4.0 link-equalization response test |

12 January 2018

PCIe 4.0 Transmitter Electrical Testing (Part II)

|

| Figure 1: With an add-in card as our DUT, we will measure the transmit signal at the root complex on the system board |

PCIe 4.0 Transmitter Electrical Testing (Part I)

|

| Figure 1: The two basic PCIe 4.0 transmitter tests are shown above outlined in green |

11 January 2018

Gearing Up for PCIe 4.0 Electrical Compliance Test

|

| Figure 1: A key element in PCIe 4.0 compliance test is a high-bandwidth, real-time oscilloscope (shown is the Teledyne LeCroy LabMaster 10Zi-A) |

Introduction to PCIe 4.0 Electrical Compliance Test

|

| Figure 1: PCI Express is now in its fourth generation and poses daunting physical-layer test challenges |

10 November 2014

PCIe 3.0 Dynamic Link EQ: De-Emphasis, Preshoot, Cursors, and Presets

|

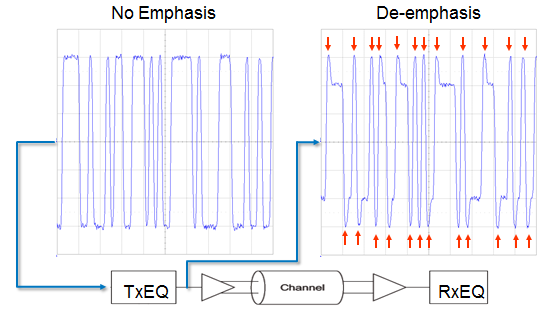

| Figure 1: De-emphasis, a key transmit-side equalization technique for PCIe 3.0, boosts high-frequency content |

06 November 2014

The Hows and Whys of PCIe 3.0 Dynamic Link Equalization

|

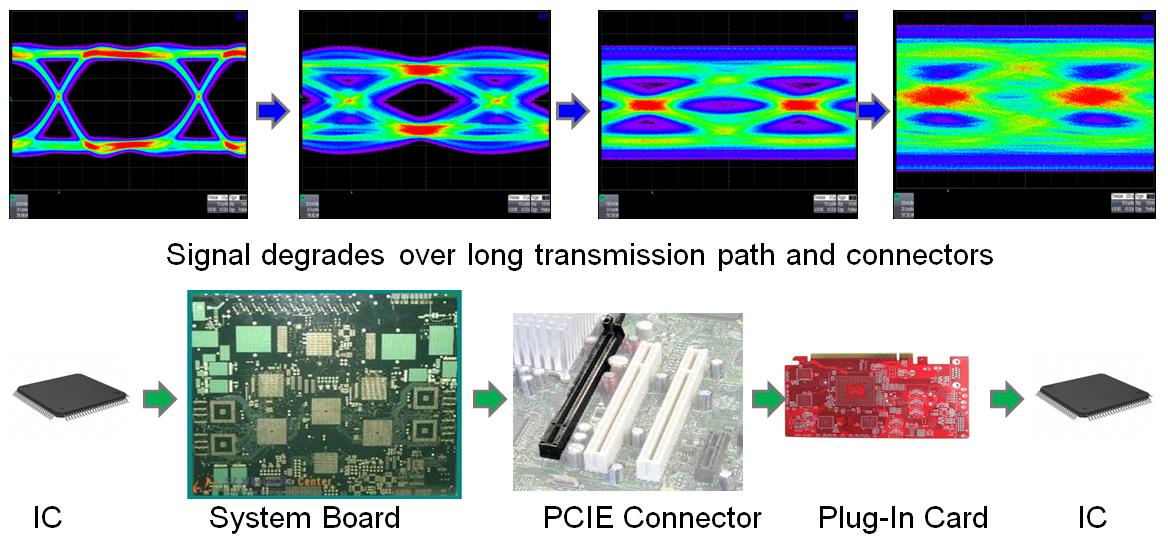

| Figure 1: SI problems are the root cause for dynamic link equalization in PCIe 3.0 |

Subscribe to:

Posts (Atom)