|

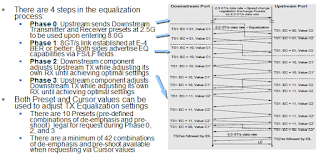

| Figure 1: A diagrammatic view of the PCIe 3.0 dynamic link training process |

You need to test, we're here to help.

You need to test, we're here to help.

Showing posts with label FIR. Show all posts

Showing posts with label FIR. Show all posts

16 January 2018

An Under-The-Hood View of PCIe 3.0 Link Training (Part II)

14 November 2014

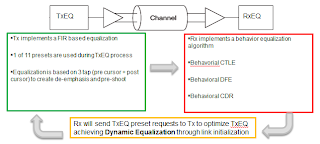

An Under-the-Hood View of PCIe 3.0 Link Training (Part I)

|

| Figure 1: An overview of the elements of PCIe 3.0 dynamic link equalization |

09 April 2014

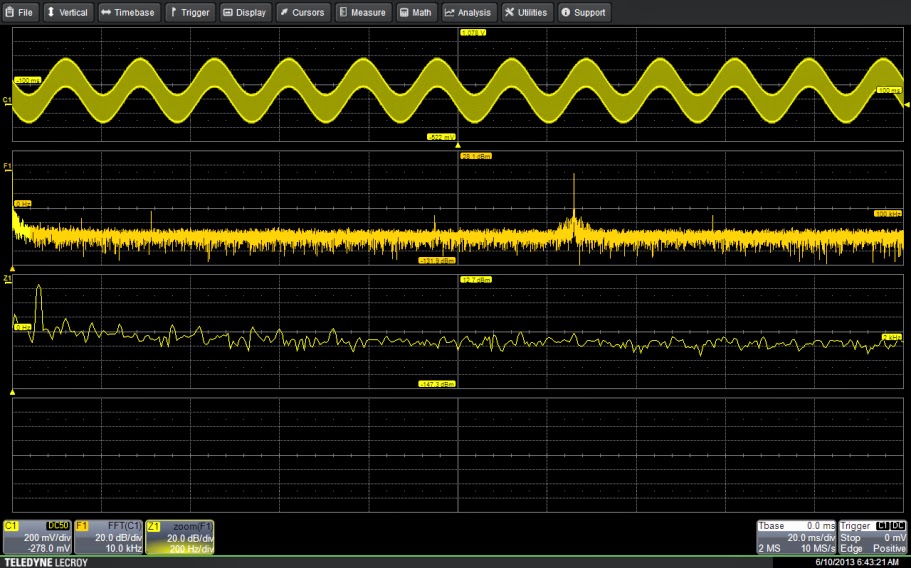

Applying Multi-Stage, Multi-Rate Digital Filtering

|

| Figure 1: The input signal shows both the desired 63-kHz signal along with a 60-Hz component. Zoom trace Z1 shows the 60-Hz component in detail. |

Subscribe to:

Posts (Atom)