|

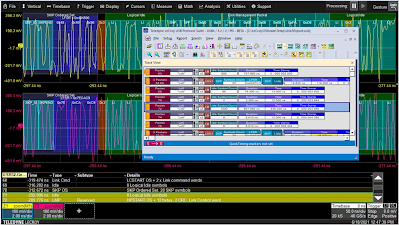

| Figure 1. USB 3.2 electrical decoding with ProtoSync view of protocol packets, captured using TF-USB-C-HS. Click on any image to enlarge it. |

TF-USB-C-HS enables you to probe all points on the USB-C connector to measure and analyze live links. The insertion-loss profile of the included cable and coupon is tuned to be the equivalent of a golden 0.8-m USB Type-C cable, so you can replace a 0.8-m cable with the coupon and not experience any difference in link performance. The coupon also has a loop to allow a current probe to make load-current measurements, and the HS version is compatible with Teledyne LeCroy DH Series probes for making high-speed differential measurements.

We'll show how to trigger, acquire and decode to find problematic link training packets synchronous with the physical-layer electrical waveforms, so you can tell if the source of your interoperability problem is electrical, logical or both.

Equipment

Required are:

- 4 Ch, ≥16 GHz, 40 GS/s real-time oscilloscope such as SDA/WaveMaster 8 Zi-B or LabMaster 10 Zi-A

- USB3.2 D decoder software option

- 16 or 20 GHz differential probe (2 each), such as DH16-PL or DH20-PL

- Voyager M310P, M310e or M4x USB Protocol Analyzer

Recommended are:

- ProtoSync option for USB (requires installation of USB Protocol Suite software)

- SDAIII-CompleteLinQ option for eye diagram analysis of the live link

Probing with the TF-USB-C-HS Test Coupon

The TF-USB-C-HS is connected between the DUT and the Exerciser/Analyzer ports of a Voyager Analyzer (M310e/M310P or M4x), using the included USB-C cable (Figure 2).

|

| Figure 2. Test setup for USB 3.x PHY-logic debug using protocol trigger. |

Signals are input to the oscilloscope by way of the test coupon:

- TX1 is input to A-row Upper Deck C1 using a DH Series differential probe.

- TX2 is input to A-row C2 using same.

- Optionally, sideband signals CC1/CC2 and Vbus can be monitored using passive probes on the B-row connectors of the oscilloscope.

- The Voyager trigger out signal is connected to oscilloscope Ext In.

Protocol Analyzer Triggering

|

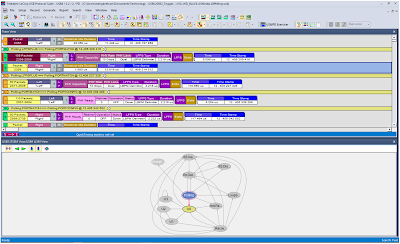

| Figure 3. Voyager protocol analyzer view of the polling state packets of the USB 3.2 LTSSM. |

For instance, during Link training, you can send a trigger pulse on SCD1, SCD2, LBPM or an LMP (Link Management Packet). As each trigger event occurs in the signal, the event is marked on the protocol trace and a pulse is sent from the Trigger Out connector of the protocol analyzer to the Ext In trigger input of the oscilloscope, enabling it to capture the electrical signals at virtually the same time.

Oscilloscope Triggering and Decoding

Set up the oscilloscope for an Edge trigger using the Ext In Source.

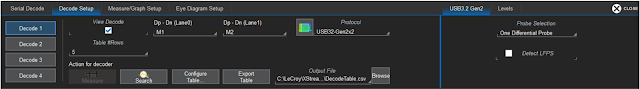

Set up the USB 3.2 D software for Gen2x2 decoding, with One Differential Probe selection. (Note that our example uses acquisitions of Lane0 and Lane1 saved to memories M1 and M2. When probed live, these signals would be on C1 and C2.)

|

| Figure 4. Setup for USB 3.2 Gen2x2 decoder. |

After acquiring, use the decoder Search or Filter feature to find the packet type of interest, which appears in the Type column of the decoder result table. Clicking that row of the table will zoom to the same time in the electrical trace. If you also have the ProtoSync display open (as in Figure 1), you'll also see exactly which protocol packet is involved.

Eye Measurements

|

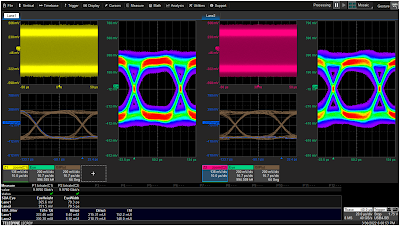

| Figure 5. Eye diagrams show signal integrity of live link during negotiations. |

If you have installed the SDAIII-CompleteLinQ oscilloscope option, a complete set of signal integrity tools is available, including jitter and eye diagram measurements and plots. You can use the eye diagrams to look at the electrical performance of the live link. If the signal is not optimized for the cable it is driving, you may see an eye diagram that has too much or too little equalization. The ISI Plot allows you to evaluate the effect of different pre-emphasis presets on the transmitted eye.

Multi-lane testing with SDAIII-CompleteLinQ also allows you to see both transmitter signals side-by-side in order to determine if there are lane-dependent SI issues that might be contributing to poor link performance.

You can download these instructions in our PDF application note, "Using TF-USB-C-HS to Debug USB 3.1/3.2 PHY-Logic and Link Training."

No comments:

Post a Comment