|

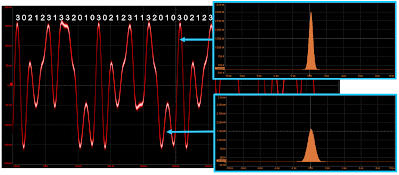

| Figure 1. The four levels and three eyes of the PCIe 6.0 PAM4 signal. Click on any image to enlarge. |

So, what can implementers expect as they retool for PCIe 6.0 Base Tx and Base Rx physical layer testing?

Higher Speeds

Each time there's a new generation of PCI Express, the data rate is basically double that of the previous generation. PCIe 6.0 continues the trend of doubling the data rate, from 32 GT/s to 64 GT/s. PCIe 6.0 devices can technically operate at any speed from 2.5 GT/s all the way up to 64 GT/s, but the PCIe compliance program tests the lower speeds such as 2.5, 5 and 8 GT/s to the 4.0 and 5.0 PHY test specifications.

New PAM4 Signaling

PCIe 6.0 manages to double the data rate without doubling the channel bandwidth requirements by using PAM4 signal modulation, which means that the throughput is increased to two bits per UI versus the one bit per UI for NRZ signaling. There are a few key differences between testing an NRZ signal and a PAM4 signal. An NRZ signal has two levels and produces one eye, whereas a PAM4 signal (Figure 1) has four levels, therefore producing three eyes. The peak-peak voltage levels for a PCIe 5.0 32 GT/s NRZ signal is the same as for a PCIe 6.0 64 GT/s PAM4 signal, but the three eyes of a PAM4 signal have a reduced eye height and eye width, which means tighter noise and jitter tolerances, one of the challenges of moving to PAM4 modulation.

Tighter Tolerances

The multi-level PAM4 signal is more susceptible and sensitive to noise, which means the jitter seen at the receiver of the device must be as low as possible to ensure linearity among all voltages levels so that the receiver can properly decide if an individual UI in the signal is a 0, 1, 2 or 3.

|

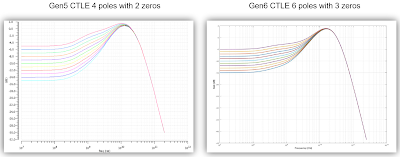

| Figure 2. Histograms of the slew rate measurement show the difference between a 0 to 1 and a 0 to 3 transition. |

PCIe Gen6 maintains the 16 GHz Nyquist frequency of PCIe Gen5, but the channel budget has tightened up a bit. The nominal channel went from 36 dB for Gen5 to 32 dB for Gen6.

New CTLE and Error Correction Methods

|

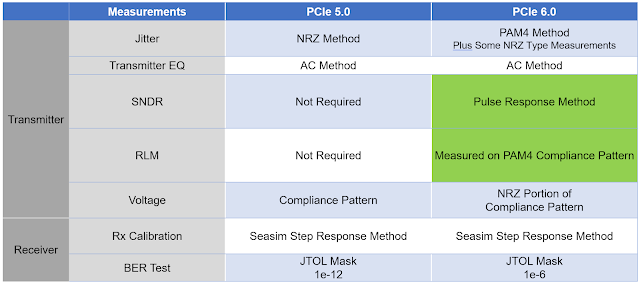

| Figure 3. Gen5 CTLE vs. Gen6 CTLE curves. Images from PCI Express Base Specification 6.0, pages 1372 and 1374. Copyright 2022 PCI-SIG®. |

The reliability of the receiver has also improved in PCIe 6.0 with the introduction of Forward Error Correction (FEC). FEC operates on the principle of sending redundant data that can be deployed to correct some errors at the receiver, while CRC is an error detection code used to detect the errors. A receiver uses the FEC to correct any errors in a FLIT, after which it applies the CRC check on the 250 bytes that are protected by the CRC. If a FLIT fails the CRC check, it is eventually corrected through the link layer retry mechanism.

New Measurements

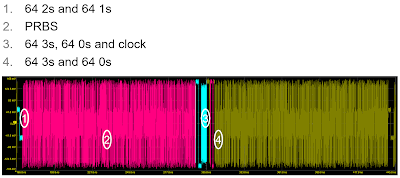

Figure 4 shows the different methods used to make each of the measurements for PCIe 5.0 and PCIe 6.0 Base testing.

|

| Figure 4. PCIe 5.0 measurements compared to PCIe 6.0 measurements. |

Signal to Noise Distortion Ratio (SNDR) and Transmitter Ratio of Level Mismatch (RLM) are two new measurements introduced in PCIe 6.0. These will be described at more length in a future post.

The oscilloscope noise impacts the SNDR of a real-life device, and the oscilloscope noise must be considered if you want to have an accurate SNDR measurement for your device. There are various possible methodologies to compensate for the oscilloscope noise contribution to the SNDR measurement, and Teledyne LeCroy's PCIe 6.0 Base test solution has implemented several of them.

New Compliance Pattern

|

| Figure 5. New PCIe 6.0 compliance pattern signal. |

New BER

PCI Express 5.0 used a BER of 1e-12, whereas PCI Express 6.0 uses a BER of 1e-6. The low-latency FEC detects and corrects certain errors, and the CRC will correct the errors not detected by FEC. Combining FEC with CRC makes error detection very reliable, which allows PCI Express 6.0 to use a BER of 1e-6..

Equipment Requirements

The equipment used for PCIe 6.0 Base testing remains, for the most part, the same as for PCIe 5.0.

Tx testing requires:

- At least 50 GHz oscilloscope, such as our LabMaster 10 Zi-A

- Breakout fixtures and cables

Rx calibration and testing requires:

- At oscilloscope, such as our LabMaster 10 Zi-A

- A high-speed BERT capable of 2.4 Gbit/s to 128 Gbit/s (PAM4 goes up to 64 Gbaud), Jitter and Noise generation, up to 10-tap Emphasis function, 12 dB CTLE and Clock Recovery functions, such as the Anritsu SQA-R MP1900A

- Breakout fixtures and cables

- A TDR, such as WavePulser 40iX, or VNA to characterize the fixtures

- Seasim software to post-process the BERT’s step response

Teledyne LeCroy’s QPHY-PCIE6-TX-RX software, now in beta, automates the entire PCIe 6.0 Base testing process—coordinating the instruments and third-party software, showing when and how to make proper connections, and running all required measurements at the appropriate limits for the device type and the speed under test. Contact Anthony.Mickens@Teledyne.com for access to our beta software or more information about our complete PCIe 6.0 Base test solution. You can also find out more at teledynelecroy.com/pcie-electrical-test/.

Watch Anthony describe the tests in more detail in the on-demand webinar, “Introduction to PCI Express 6.0 PAM4 Physical Layer Testing”.

See also:

Debugging L1 Substates Timing Errors with CrossSync PHY for PCIe

PCI Express 4.0 Error Detection Using a BERT and Oscilloscope

PCIe Electrical Testing: Where Are We?

No comments:

Post a Comment