|

| Figure 1. PCIe specifications through Rev 5.0. |

You may be wondering where we are in the roll out of PCI Express test specifications and active testing. Figure 1 shows the status as of March, 2020.

Each generation of PCIe evolves through a similar standard specification process:

- A Base specification defines fundamental device behavior, from physical layer through protocol operations. At the physical layer, this describes characteristics like voltage swing, timing, jitter, etc. as measured at the Tx and Rx pins of the chip.

- One or more physical interface specifications (e.g., CEM) define interfaces where two devices from different vendors can interoperate. Like the Base specification, this usually describes characteristics like voltage swing, timing, jitter, etc., only as they are measured at the connector.

- One or more Compliance Test Specifications (CTS), usually one for each interface specification) give precise descriptions of how to test for compliance to the standard.

- A Compliance Program tests devices in a controlled environment, and passing devices are certified as compliant to the standard in question.

With Rev 5.0 of the PCIe Base specification released mid-year 2019, we should soon see the first official release of the Rev 5.0 CEM and Test specifications, which are still in draft. But who is actually testing PCIe 5.0 devices? At this point, it is primarily chip and IP designers who are actively testing to the PCIe 5.0 Base specification in preparation for forthcoming CEM tests.

Here, we’ll summarize the principal ways in which PCIe 5.0 Base specification testing departs from the 4.0 version and the test equipment required to test to the new standard.

PCIe 5.0 Electrical Test Equipment

The PCIe specification is explicit about the requirement to use a real-time oscilloscope, not a sampling oscilloscope, to perform test measurements. PCIe Rev 5.0 requires a 50 GHz bandwidth oscilloscope, such as our LabMaster 10 Zi-A. The LabMaster can software limit bandwidth as required to test backward compatibility to lower-speed PCIe standards. PCIe Rev 6.0 on the horizon will likely use 32 Gbaud PAM4 signaling, which instead of increasing the bandwidth required to support higher-speed signals will instead change the number of bits in a symbol, so the same LabMaster that serves for PCIe 5.0 will also serve for PCIe 6.0.Eye diagram and jitter analysis, channel emulation (embedding) and fixture de-embedding are also required capabilities for PCIe testing, all performed by our SDAIII-CompleteLinQ software, which runs on the LabMaster.

Another critical tool for PCIe electrical testing is a Bit Error Rate Test instrument, or BERT, which is used not only for receiver (Rx) testing but for any Link Equalization testing that requires a negotiation with the device under test (DUT). The BERT must be protocol-aware so that it can negotiate Link training operations and loop-back with the DUT. Teledyne LeCroy has partnered with Anritsu Corporation to integrate their SQA-R MP1900A BERT into our PCIe 3.0, 4.0 and 5.0 solutions. Our QualiPHY PCIe 5.0 compliance software, QPHY-PCIE5-TX-RX, automates calibration and testing among the oscilloscope, MP1900A and DUT.

Many PCIe 4.0 and 5.0 tests require the characterization of a loss channel, which can be done using S-parameters measured by the WavePulser 40iX.

Testing to the Base Specification

|

| Figure 2. PCIe 5.0 test boards for devices with embedded clock (left) and reference clock (right). |

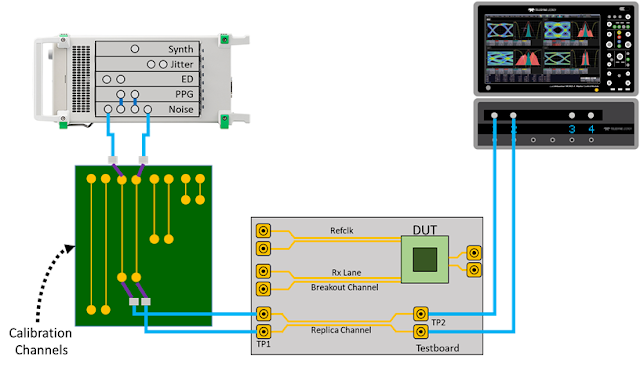

Both types of PCIe test boards include a replica channel that should be electrically identical to the breakout channel. Knowledge of the replica channel (e.g., an S-parameter file) is used to de-embed the breakout channel and test cables such that the measurement is made directly at the Tx pins. Figure 3 diagrams the process as it would be accomplished using the Teledyne LeCroy solution.

|

| Figure 3. Process of de-embedding the break out channel from Tx measurements. |

It is also possible to derive an S-parameter model of the test channel from simulation in the absence of a physical replica channel.

Base Transmitter Tests

|

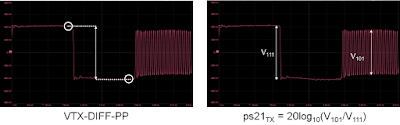

| Figure 4. PCIe 5.0 transmitter measurements VTX-DIFF-PP and ps21TX on a 16 GHz signal. |

- VTX-DIFF-PP measures the transmitter differential peak-peak voltage after settling to the nominal 1 level and 0 level. Many signal repetitions are averaged to reduce the effects of uncorrelated noise.

- Ps21TX measures actual package insertion loss after de-embedding the channel back to the pins. The signal used has a low-frequency section representing a DC amplitude (V111) followed by a high-frequency section representing the signal amplitude at 16 GHz (V101). The ratio of those yields an estimate of the insertion loss of the package at 16 GHz.

Base Receiver Tests

The PCIe 5.0 receiver-side test philosophy is to first create a signal that behaves as would a worst-case compliant transmitter with correct emphasis levels and maximum allowed jitter and noise. Then, impair the signal as much as possible by adding channel loss, only adding jitter and noise as a last resort to fine-tune eye closure.Why this approach? The PCIe environment allows for quite long channels between devices, with large amounts of loss, and this is the dominant impairment in real-world use. Figure 5 shows a PCIe 5.0 nominal channel, where up to 36 dB of total system loss is expected between the root complex and the endpoint. Simply adding lots of jitter and noise to close the eye does not result in the same kind of impairment and does not stress the DUT in a realistic way.

|

| Figure 5. PCIe 5.0 nominal channel has up to 36 dB total system loss at 16 GHz. |

Prior to measuring the signal at the receiver, PCIe 5.0 Base receiver testing involves calibrating the signal generator to approximate this worst-case transmitter signal at different emphasis levels until the specified “stressed” eye height and width are found, which can be a tediously repetitive procedure. The Teledyne LeCroy receiver test process, fully automated by the QualiPHY software working with the oscilloscope and Anritsu BERT (Figure 6), is to:

- Use the oscilloscope to calibrate signal at BERT output for correct emphasis presets and maximum jitter permitted in a compliant transmitter.

- Add an appropriate loss channel using a variable ISI board such that the transmitter and receiver equalization are both working as hard as possible to recover an open eye at the receiver (simulated by the oscilloscope), where the eye width and height are barely above the target at the receiver.

- Add impairments (jitter, noise) at the BERT to achieve target EH/EW values at the receiver.

- Remove the oscilloscope and place the DUT in system – allowing the DUT to negotiate correct transmitter equalization.

- Perform receiver jitter tolerance tests against a BER mask at frequencies up to 100 MHz.

|

| Figure 6. PCIe receiver calibration replicates a worst-case transmitter signal. |

The DUT may be induced to loop-back manually or using a state machine, but it is not required for Base testing as it would be for a Compliance test.

More information about PCIe Rev 5.0 Base testing, as well as forthcoming CEM testing, is available in the on-demand webinar, PCIe Electrical Test Webinar—From 8 GB/s to 32 GB/s and Beyond.

No comments:

Post a Comment