|

| Figure 1. The RP2060 and RP4060 build on the legacy of the RP4030 power rail probe. The new probes are ideally suited to working with the new 48 Vdc power structures. |

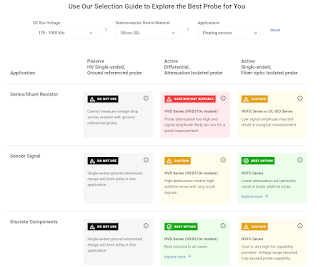

Recently, we released two, new power rail probes that build on those capabilities—the 2 GHz RP2060 and 4 GHz RP4060. Both probes feature:

- ±60 V Offset Capability

- ±800 mV Dynamic Range

- 50 kΩ DC Input Impedance (for low loading of low-impedance power rails)

- 1.2:1Attenuation (for low additive noise)

- MCX-terminated cable with a variety of board connections: 4 GHz*-rated MCX PCB mount;

4 GHz* solder-in; 3 GHz* coaxial cable to U.FL PCB mount; optional 500 MHz browser

Why the New Probes?

One driver of the new release is the increase in the number and size of data centers needed to support cloud computing and other data-intensive applications, and the new power architectures they require. The new rail probe is designed to ideally meet the needs of engineers working with power rails rated up to 48 Vdc.