|

| Figure 1: The track math function shows how data changes over time |

31 January 2018

Getting The Most Out Of Your Oscilloscope: Tracks and Trends

30 January 2018

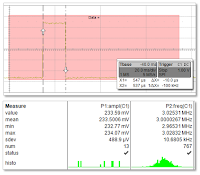

Getting The Most Out Of Your Oscilloscope: Cursors and Parameters

|

| Figure 1: Cursors (top) and parameter measurements (bottom) are both powerful tools in their own right |

29 January 2018

Getting The Most Out Of Your Oscilloscope: Documentation

|

| Figure l: A LabNotebook entry quickly and easily saves everything you need to later replicate your measurements |

Getting The Most Out Of Your Oscilloscope: Trigger Delay

|

| Figure 1: Pre-triggering, or trigger delay, is a useful tool for debugging applications |

26 January 2018

Getting The Most Out Of Your Oscilloscope: Navigation With MAUI

|

| Figure 1: Oscilloscope UIs such as Teledyne LeCroy's MAUI provide tons of shortcuts and touch gestures |

Getting The Most Out Of Your Oscilloscope: Setup

|

| Figure 1: Choosing a effective sample rate is key to seeing the finer details of a waveform |

24 January 2018

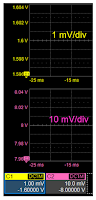

Making On-Die Power-Rail Measurements (Part III)

|

| Figure 1: This screen capture shows the idle-state conditions |

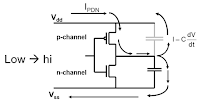

Making On-Die Power-Rail Measurements (Part II)

|

| Figure 1: When switching from low to high, PDN noise flows from the Vdd rail through to the Vss rail |

Making On-Die Power-Rail Measurements (Part I)

|

| Figure 1: Our test setup for the on-die measurement examples |

Measuring Shared On-Die Power Rails

|

| Figure 1: This schematic represents the signal paths in typical, general-purpose I/Os |

22 January 2018

Setting the Stage for On-Die Power-Rail Measurements

|

| Figure 1: Measuring on-die Vdd rail noise requires a suitably instrumented die and package |

Power-Rail Noise: Small Signal, Big DC Offset

|

| Figure 1: Your scope's vertical adjust has its limits |

19 January 2018

Bandwidth vs. Current Load in Power-Rail Measurements

|

| Figure 1: Connecting a 6" length of coaxial cable between a low-impedance power rail and a 1-MΩ input impedance produces reflections and ringing artifacts on your signal acquisition |

18 January 2018

How 10X Attenuating Probes Kill Signal-to-Noise Ratio

|

| Figure 1: Signal waveforms captured using a 10X attenuating probe (top) and a BNC probe (bottom) with tips open |

Understand RF Pickup When Measuring Power Rails

|

| Figure 1: Teledyne LeCroy's HDO8108A sports a very low noise floor of about 145 μV |

17 January 2018

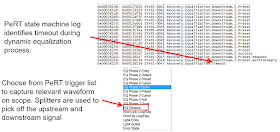

Some More PCIe 3.0 Test Examples (Part II)

|

| Figure 1: This shows how a PeRT 3 state-machine log can be invaluable in diagnosing timeouts in requests for presets |

Some PCIe 3.0 Test Examples (Part I)

|

| Figure 1: Protocol and electrical views of slow electrical response to a preset request |

A Tour of a PCIe 3.0 Test Setup

|

| Figure 1: Test-equipment requirements for PCIe 3.0 |

16 January 2018

An Under-The-Hood View of PCIe 3.0 Link Training (Part II)

|

| Figure 1: A diagrammatic view of the PCIe 3.0 dynamic link training process |

PCIe 4.0 PLL Bandwidth Testing

|

| Figure 1: PLL bandwidth testing ensures that the add-in card's PLL bandwidth and peaking are within specifications |

15 January 2018

PCIe 4.0 Receiver Link-Equalization Testing (Part II)

|

| Figure 1: Working out the optimal combination of Tx emphasis presets and receiver CTLE settings |

PCIe 4.0 Receiver Link-Equalization Testing (Part I)

|

| Figure 1: PCIe 4.0 receiver link-equalization testing takes place at the site of the channel's worst-case signal |

PCIe 4.0 Transmitter Link-Equalization Testing

|

| Figure 1: Shown is an overview of the PCIe 4.0 link-equalization response test |

12 January 2018

PCIe 4.0 Transmitter Electrical Testing (Part II)

|

| Figure 1: With an add-in card as our DUT, we will measure the transmit signal at the root complex on the system board |

PCIe 4.0 Transmitter Electrical Testing (Part I)

|

| Figure 1: The two basic PCIe 4.0 transmitter tests are shown above outlined in green |

11 January 2018

Gearing Up for PCIe 4.0 Electrical Compliance Test

|

| Figure 1: A key element in PCIe 4.0 compliance test is a high-bandwidth, real-time oscilloscope (shown is the Teledyne LeCroy LabMaster 10Zi-A) |

Introduction to PCIe 4.0 Electrical Compliance Test

|

| Figure 1: PCI Express is now in its fourth generation and poses daunting physical-layer test challenges |

04 January 2018

Probing Techniques and Tradeoffs (Part VI): Dynamic Range

|

| Figure 1: Differential-mode dynamic range is the maximum allowable voltage between the probe amplifier's inputs |